# ISSN: 2321-2152 IJMECE International Journal of modern

electronics and communication engineering

E-Mail editor.ijmece@gmail.com editor@ijmece.com

www.ijmece.com

ISSN2321-2152www.ijmece .com

Vol 9, Issue 2 Apr 2021

### Full-Bridge PWM Converter with Auxiliary Active Clamp for Zero-Voltage and Zero-Current Switching

<sup>1</sup>Dr.K.Suneeta, <sup>2</sup>Mis.B.Prashanthi, <sup>3</sup>Mr.B.Raju

AbstractAn improved presentation of the previously presented ZVZCS FB PWM converters has been offered with the development of a new ZVZCS FB PWM converter. It is possible to achieve ZVS (for driving leg switches) and ZCS (for slacking leg switches) without the use of lossy components or the saturable reactor by integrating an optional dynamic cinch and managing the brace switch properly. The novel converter is attractive for high-voltage and high-power (>10 kW) applications because of its many advantages, such as its fundamental circuit architecture, high efficacy, and simplicity. The rules of action are explained and analysed. A 1.8-kW 100-kHz shielded entryway bipolar transistor (IGBT)-based exploratory circuit is used to demonstrate and test the novel converter's features and design considerations.

Index Terms—DC–DC power conversion.

#### **INTRODUCTION**

IGBT's are commonly utilised in switching power conversion applications because of their specific benefits, such as their ease of driving and high frequency switching capabilities. The newest IGBTs can function at 10–20 kHz without a snubber circuit because to ongoing improvements in their performance. It's also being replaced by IGBT's for applications that need several or a few kilowatt of power since IGBT's are more suited to handling high-voltage and high-power applications than MOSFET's. Due to IGBT's tail-current characteristic, their maximum working frequency is restricted to 20–30 kHz [1]. It is necessary to lower the turn-off switching loss in IGBTs in order to operate them at high switching frequencies. An external snubber capacitor or zerocurrent switching (ZCS) may be a solution to this problem. If you're looking for an efficient way to get rid of a carrier, you'll want to go with ZCS. It's no secret that ZVS full-bridge pulsewidth modulation converters have garnered a lot of attention [2-5]. The ZVS conditions for the switches are provided through a phase-shifted PWM approach that utilises all of the bridge's parasitic parts. For highfrequency, high-power applications, ZVS with no extra components and low-device voltage/current stresses make it a highly appealing alternative to MOSFETs. It's unlikely that IGBTs would work well with the ZVS FB PWM converter because to the relatively small ZVS range, unless the leakage inductance is really big.

Professor, Assistant Professor Assistant Professor

Department of EEE Engineering, Pallavi Engineering College, However, Defects like as duty-cycle loss and parasitic ringing in the secondary restrict the converter's highest possible power rating, as well. A ZVZCS FB PWM converter [7] used IGBTs for a high-frequency converter. All principal switches employ IGBTs with no antiparallel diodes. IGBTs on the leading leg give the ZCS state to IGBTs on the trailing leg during freewheeling, thus the main current is reset using reverse avalanche-breakdown

using a new technique [8]. During the freewheeling phase, the primary current is reset using a dc blocking capacitor and a saturable inductor in the primary, resulting in ZCS state for the lagging-leg switches. ZVS is still being used to control the switches on the leading leg. The dc blocking capacitor is used to recover the energy from the leakage inductance, which is then sent to the load. Even though the leakage inductance is quite big, broad duty-cycle control range may be achieved by raising the blocking capacitor voltage (i.e., lowering the capacitance of the blocking capacitor). It is possible to use this converter in power ranges of many kilowatts. Some drawbacks, such as the loss of saturable inductance and its cooling issue, prevent the power output from rising over 10 kW. " Figure 1 shows the ZVZCS-FB PWM converter proposed in this study to enhance the performance of ZVZCS-FB PWM converters previously published [7, 8]. As with converters [2-5], [8], leading-leg switches implement ZVS. In lagging-leg switches, how can you get ZCS? а

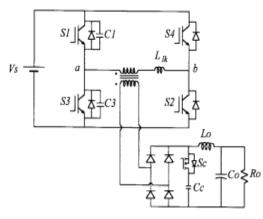

Fig. 1 depicts the proposed ZVZCS FB PWM converter circuit architecture.

A secondary rectifier with an active clamp and modest control is the only way to do this. To accomplish ZVZCS functioning, no lossy components are used. A high voltage is given to voltage. There are, however, a few downsides to this option. There is no remaining stored energy in the leakage inductance after the leading-leg IGBT's. During the freewheeling phase, there is parasitic ringing in the primary. Low and fixed reverse avalanche-breakdown voltage limits duty cycle control to 15–30 V. Unless the leakage inductance is very low, the overall efficiency of the circuit will be significantly reduced. The ZVZCS FB PWM converter was provided

the leakage inductance (greater than the input voltage) to reset the primary current during the freewheeling period, thus the duty cycle loss is nearly insignificant. New converter addresses most of the disadvantages of soft-switching FB PWM converters, making the new converter particularly suitable for high-voltage applications where IGBT's are the primary power switches. converter's The suggested fundamental functioning and characteristics are shown. For testing purposes, an IGBT-based 100 kHz prototype has been created and tested, including a MOSFET for the clamp switch..

#### **II. OPERATION AND ANALYSIS**

Although the active clamp is on the secondary side, the fundamental construction of the ZVZCS FB PWM converter is identical to the ZVS FB PWM converter [3]. Phase-shift PWM control is used to control the principal switches. Later in this section, we'll go over how to regulate the active clamp. The following assumptions are made to demonstrate steady-state functioning.

1) Everything is perfect.

During a switching period, the output filter inductor is big enough to serve as a continuous current source.

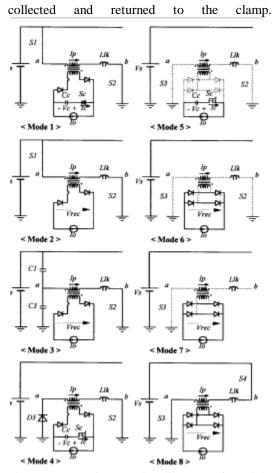

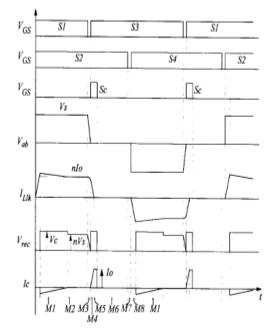

Because of its size, a clamp capacitor may be used as a steady-state voltage source during a switching operation. Within each half-cycle of operation, the new converter offers eight different working modes. Figures 2 and 3 illustrate the corresponding circuits and operating waveforms, respectively.

A. The input power is transferred to the output via the conductivity of Mode 1. In this mode, the rectifier voltage is capped by the body diode through which it was growing. By resonating with the parasitic capacitance, the leakage inductance generates energy that may be

Fig. 2. Operation mode diagrams for eight modes.

capacitor. So, the primary current is decreased as follows:

$$I_p(t) = \frac{1}{L_{\rm lk}} \left( V_s - \frac{V_c}{n} \right) \cdot t \tag{1}$$

where  $\eta$  is the transformer turns ratio and the clamp capacitor current can be expressed as follows:

$$I_c = \frac{I_p}{n} - I_o.$$

(2)

This mode ends when Ic becomes zero. The duration of this mode depends on the leakage inductance and the junction capacitance and the reverse recovery time of the rectifier diodes.

#### B. Mode 2

The body diode of Sc blocks and the secondary rectifier voltage becomes

$$V_{rec} = nV_s.$$

(3)

S1 and S2 are still on and the powering mode is sustained during this mode.

C. Mode 3 According to the given duty cycle,S1 is turned off and then the reflected load current to the primary chargesC1 and dischargesC3. The switch voltage increases linearly as follows:

$$V_{S1}(t) = \frac{nI_o}{C1 + C3} \cdot t. \tag{4}$$

The turn-off process of S1 is low loss if the external capacitor is large enough to hold the switch voltage at near zero during the switch turn-off time. During this mode, the secondary rectifier voltage is also decreased with almost same rate. At the end of this mode, D3 is turned on.

**D. Mode 4** After D3 starts conducting,S3 can be turned on with ZVS. The load current freewheels through the primary side, D3 and . To reset the primary current, the clamp switch is turned S2 on and then the rectifier voltage becomes .Vc This voltage is applied to the leakage inductance, the primary current is linearly decreased with the slope of  $V_c/nL_{\rm Ik}$ , and  $I_c$  is linearly increased satisfying (2). The primary current reaches zero at the end of this mode.

**E. Mode 5** The rectifier diodes are turned off since the primary current is zero and Sc is still on. During this mode, the primary current sustained at zero and Cc supplies whole load current.

**F. Mode 6** TheSc is turned off and then the rectifier voltage is dropped to zero. The load

current freewheels through the rectifier itself. No current flows through the primary.

**G. Mode 7** Sc is turned off with ZCS. No tail current exists since all minority carriers are eliminated by recombination. This mode is dead time between S2and S4.

**H. Mode 8** At the end of freewheeling mode,S4 is turned on. This turnon process is also ZCS since the primary current cannot be increased abruptly and no diode reverse recovery is involved. The primary current Ip is linearly increased with the slope of  $V_s/L_{\rm Ik}$ . The rectifier voltage is still zero. This is the end of an operating half cycle.

## III. FEATURES OF THE PROPOSED CONVERTER

A. Effective Soft Switching (ZVZCS[7, 8] ZVZCS converters use the same soft switching method (ZVS for leading-leg switches and ZCS for lagging-leg switches) introduced in [7, 8]. ZCS for lagging-leg switches is achieved using lossy components in the converters [7, 8]. Freewheeling mode [7] or the core loss of a saturable reactor [8] both totally dissipate the stored energy in the leakage inductance of the leading-leg IGBTs. If the passive clamp circuit is used to clamp the secondary rectifier voltage, extra loss is included in the clamp resistors for both converters. There is a restricted power range for both converters as a result (several kilowatts). To improve ZCS performance for lagging-leg switches, the converter's active clamp is controlled differently than in the current design [3]. There are no lossy components or parasitic ringing in the secondary rectifier in order to achieve ZCS. As a result, the converter under consideration is capable of handling a greater power level (10 kW). For lagging-leg switches, a broad load range allows for ZCS, whereas for leading-leg switches, a wide load range allows for ZVS. Similarly, [7] and [8] have the same ZVS and ZCS ranges.

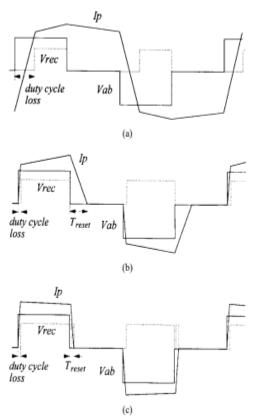

**B.** More Reduced Conduction Loss This converter's main voltage, current, and voltage are compared to the ZVS [2]–[5], and ZVZCS [7]–[8], as seen in Figure 4. In order to have a suitable ZVS range, the ZVS converter needs to have a substantial leakage inductance. It is unnecessary to use a high leakage inductance with ZVZCS converters [7, 8] since they remove freewheeling current from the primary and reduce duty-cycle loss. When the main current reset time Treset is equal to the applied voltage to the leakage inductance VLik during

freewheeling, the maximum duty cycle is governed by this equation:

Since the ZVZCS converters in [7] and [8] have a low reverse voltage, they have a significant output current (several tens of volts)

A comparison of the simplified voltage and current waveforms of primary and secondary rectifiers is shown in Figure 4. ZVS PWM converter (a). ZVZCS PWM converters [7, 8] are an alternative. Proposed converter (c)

is used to the duty-cycle loss known as leakage inductance. The large reverse voltage is supplied to the leaking inductance in the proposed ZVZCS converter, resulting in a tiny Treset. As a result, the suggested converter's overall efficiency is enhanced because to its low dutycycle loss and modest Treset.

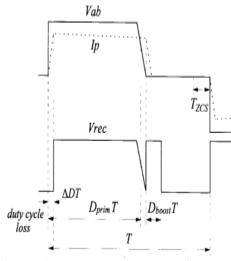

**C. Duty-Cycle Boost Effect** Secondary rectifier duty cycles are often lower than main rectifier duty cycles due to duty-cycle loss. Figure 5 shows that in the proposed converter, the primary's duty cycle might be greater than the rectifier's duty cycle. Duty-cycle boost effect is the term given to this occurrence. The workcycle is An increase in performance may be achieved by activating the active clamp at the beginning of freewheeling. The energy from the leakage inductance may be collected by employing a duty cycle boost and then supplied straight to the load through the clamp capacitor. IGBTs are used to implement the main switches in ZVZCS converters, which is a necessary functionality. The primary duty cycle is lower than MOSFET-based ZVS converters because to the shorter dead time required to complete a full ZCS turn off of the lagging-leg switches. IGBTs take a long time to recombinate their minority carriers. However, the duty-cycle boost effect allows for a near-unity increase in the effective duty cycle of the proposed converter. Obligation in the real world

Fig. 5. Primary and secondary rectifier voltage waveforms.

cycle of the proposed converter can be expressed as follows:

$$D_{\text{eff}} = D_{\text{prim}} - \Delta D + D_{\text{boost}}$$

(6)

where  $\Delta D$  is the duty-cycle loss. The Dboost is determined directly by the turn-on time of the clamp switch. The duty cycle boost effect also helps to improve the overall efficiency.

#### **IV. DESIGN CONSIDERATIONS**

**A. Decision of Dead Times** An appropriate dead time is required for both leading- and lagging-leg switches to achieve maximum performance.

1) Dead Time for Leading-Leg Switches: The dead time for leading-leg switches is determined by two factors—the ZVS range and maximum duty cycle of the primary side. The minimum dead time is determined by ZVS range as follows:

$$T_{d,\text{lead}} \ge (C1 + C3) \frac{V_s}{nI_{o,ZVS}}$$

(7)

Where Io, ZCVS is given ZVS range as one of design parameters. The maximum dead time is limited by the maximum duty cycle of the primary side.

2) Dead Time for Lagging-Leg Switches: The minimum dead time of lagging-leg switches is determined by the timeTZCS to achieve a complete ZCS of the lagging-leg switches as follows:

$$T_{d,lag} \ge T_{ZCS}$$

(8)

where the Tzsc is the minority carrier recombination time of IGBT's. The maximum dead time is also limited by the maximum duty cycle of the primary side.

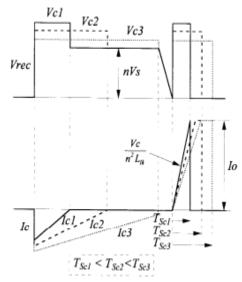

**B.** Decision of Clamp Switch On Time The illustrative waveforms of the secondary rectifier voltage and the clamp capacitor current according to the turn-on time of Sc are depicted in Fig. 6. To achieve a complete ZCS of lagging-leg switches, the primary current should be reset. The

Fig. 6. Illustrative waveforms of the rectifier voltage and the clamp capacitor current.

Fig. 7. Circuit diagram of the active clamp circuit for a center-tapped transformer. required turn-on time Tsc of Sc is obtained as follows:

$$T_{Sc} \ge \frac{n^2 L_{Ik}}{V_c} I_{o,max}$$

(9)

The clamp capacitor is charged up during powering period and discharged by turning on of Sc as shown in Fig. 6. The discharging current is quickly increased with the slope depicted in Fig. 6 and stays constant after it reaches load current Io . The increasing rate of discharging current is the same as the decreasing rate of the primary current. If the turn-on time of Sc is increased, the clamp capacitor voltage Vc is decreased and more current flows through the clamp capacitor as shown in Fig. 6. Therefore, Tsc needs to be kept as small as possible to reduce the conduction loss of clamp switch and in turn allow use of a small switch for Sc. The clamp capacitor voltage is regulated automatically as shown in Fig. 6.

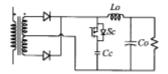

**C.** Active Clamp Circuit for Center-Tapped Transformer The proposed ZVZCS power conversion technique can also be applied for the center-tapped transformer as shown in Fig. 7. The basic operation principle is exactly the same as that of the simple output transformer except diode voltage.

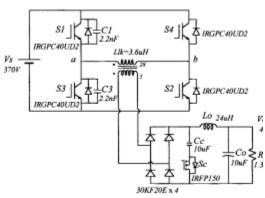

Fig. 8. Experimental circuit diagram of the proposed converter.

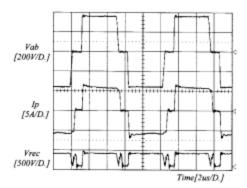

Fig. 9. Experimental waveforms of primary voltage and current and secondary rectifier voltage.

#### V. EXPERIMENTAL RESULTS

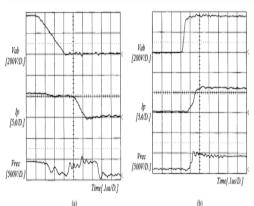

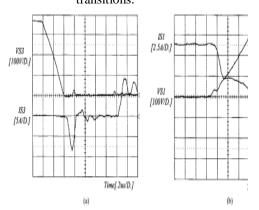

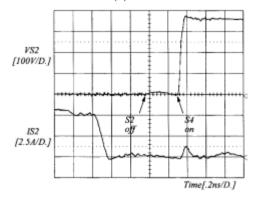

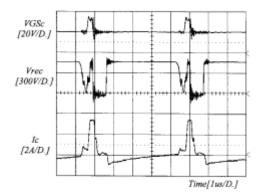

An experimental prototype of the proposed ZVZCS FB PWM converter has been created and tested in order to demonstrate the working concept. Part numbers and circuit characteristics may be seen in Fig. 8 of the experiment's schematic. The transformer has a 28:5 turn ratio and is constructed with an EE/55/55 core. At the switching frequency, a 3.6 uH leakage inductance was found. The major switches IRGPC40UD2 IGBTs. employ The IRGPC40UD2 data sheet recommends a switching frequency of 10-20 kHz. The efficiency of these IGBTs may be shown by operating them at 100 kHz. Figure 9 shows the main voltage and current waveforms, as well as the secondary rectifier voltage under maximum load (a nominal duty cycle of 0.78) and Figure 10 depicts the extended waveforms during the switching transitions of the leading and lagging legs of the rectifier. In all cases, the waveforms are perfectly in sync with the predicted ones Due to the external capacitors supplied to the leading-leg switches, the main voltage has a sluggish downslope and a quick upslope. It is estimated that duty-cycle loss will be 0.1 s or less. After the primary voltage drops to zero, the primary current is promptly restored and maintained during the freewheeling period. Only 0.15 s is required to do a main current reset. The active switch has a turn-on time of roughly 0.35 us. Extensive switching is seen in Fig.

Fig. 11. Extended ZVS switching waveforms of leading-leg switches: (a) turn on and (b) turn off.

### Fig. 12. Extended ZCS waveforms of lagging-leg switches.

waveforms of leading-leg switches. It can be seen that the antiparallel diode current flows for a short time and stays zero, and, thus, a complete ZVS turn on is achieved. The tail current is seen, but the turn-off switching loss is remarkably reduced comparing to hard switching since the rising slope of the switch voltage is slow. The ZVS range for the leading-leg switches is about 20% of full load. Fig. 12 shows the extended

### Fig. 13. Waveforms of secondary active clamp.

switching waveforms of lagging-leg switches. It can be seen that a complete ZCS turn off is achieved since the primary current is zero during the whole freewheeling period and the turn-on process of the other switch is almost ZCS. Small pulse current during turn-on transition is the charging current of the switch output capacitor. Fig. 13 shows the waveforms of the secondary active clamp. The clamp switch is turned on for a

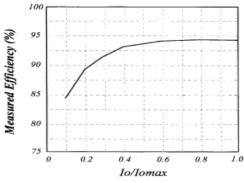

Fig. 14. Measured efficiencies.

very short time compared to the operating period (7%). The rectifier voltage waveform is a little noisy since the clamp switch operates under hard switching. The clamp capacitor current waveform is the same as the expected. Fig. 14 shows the measured efficiencies of the proposed ZVZCS FB PWM converter. The maximum overall efficiency is about 94% at full load. The efficiency improvement is not much comparing to the previous ZVZCS converter [8], but it will be considerable at higher power (> 10 kW) applications.

#### VI. CONCLUSION

An experimental prototype of the proposed ZVZCS FB PWM converter has been created and tested in order to demonstrate the working concept. Part numbers and circuit characteristics may be seen in Fig. 8 of the experiment's schematic. The transformer has a 28:5 turn ratio and is constructed with an EE/55/55 core. At the switching frequency, a 3.6 uH leakage inductance was found. The major switches IRGPC40UD2 IGBTs. employ The IRGPC40UD2 data sheet recommends a switching frequency of 10-20 kHz. The efficiency of these IGBTs may be shown by operating them at 100 kHz. Figure 9 shows the main voltage and current waveforms, as well as the secondary rectifier voltage under maximum load (a nominal duty cycle of 0.78) and Figure 10 depicts the extended waveforms during the switching transitions of the leading and lagging legs of the rectifier. In all cases, the waveforms are perfectly in sync with the predicted ones Due to the external capacitors supplied to the leading-leg switches, the main voltage has a sluggish downslope and a quick upslope. It is estimated that duty-cycle loss will be 0.1 s or less. After the primary voltage drops to zero, the primary current is promptly restored and maintained during the freewheeling period. Only 0.15 s is required to do a main current reset. The active switch has a turn-on time of roughly 0.35 us. Extensive switching is seen in Fig. REFERENCES

[1] IGBT Designer's Manual, International Rectifier, El Segundo, CA, 1994.

[2] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "Design considerations for high-voltage high-power full-bridge zerovoltage-switched PWM converter," in IEEE APEC Rec., 1990, pp. 275–284.

[3], "High voltage high power ZVS full bridge PWM converter employing active snubber," in IEEE APEC Rec., 1991, pp. 158–163.

[4] R. Redl, N. O. Sokal, and L. Balogh, "A novel soft switching full bridge dc/dc converter: Analysis, design considerations, and experimental results at 1.5 kW, 100 kHz," in IEEE PESC Rec., 1990, pp. 162–172.

[5] A. W. Lotfi, Q. Chen, and F. C. Lee, "A nonlinear optimization tool for the full

bridge zero-voltage-switched PWM dc/dc converter," in IEEE APEC Rec., 1992, pp. 1301–1309.

[6] G. Hua, E. X. Yang, Y. Jiang, and F. C. Lee, "Novel zero-currenttransition PWM converters," in IEEE PESC Rec., 1993, pp. 538–544.

[7] K. Chen and T. A. Stuart, "1.6 kW, 110 kHz dc/dc converter optimized for IGBT's," IEEE Trans. Power Electron., vol. 8, no. 1, pp. 18–25, 1993.

[8] J. G. Cho, J. Sabate, G. Hua, and F. C. Lee, "Zero voltage and zero current switching full bridge PWM converter for high power applications," in IEEE PESC Rec., 1994, pp. 102–108.