# ISSN: 2321-2152 IJMECE

International Journal of modern electronics and communication engineering

E-Mail editor.ijmece@gmail.com editor@ijmece.com

www.ijmece.com

Gan

ISSN2321-2152 www.ijmece.com

Vol 8, Issuse.4 Oct 2020

## RESOLUTION TWO-STEP TDC CMOS BY PULSE-SHRINKING FINE STAGE, BUILT-IN COARSE GAIN CALIBRATION

Erugu Krishna<sup>1</sup>, Dr.M.Bal Raju<sup>2</sup>, Dr.Palla Karunakar Reddy<sup>3</sup>, Dr.Ch Ramesh Kumar<sup>4</sup>,

#### Abstract:

This article proposes a computerized converter (TDC) solution that can meet a broad range of knowledge and fine-time goals at the same time. The proposed TDC utilizes a beat contracting (PS) plot for a precise target and two-advance (TS) engineering for a larger range in the second phase. The suggested PS TDC solves the undesired non-uniform contracting rate issue that plagues conventional PS TDCs by using an assumed counterbalance beat and a balance beat width detecting method. Due to sign spread and extension fraud between coarse and fine phases, the proposed TS architecture achieves nonlinearity with a few methods, resulting in an inferred coarse increase adjustment mechanism. The replication findings in a 0.18-m normal CMOS innovation show 2.0-ps targets and 16-piece go connected to 130-ns input time interim of 0.08-mm2 area in a TDC modification. With an 18.0 maws 1.8-V supply, it has a single-shot accuracy of 1.44 ps and operates at 3.3 MS/s.

Built-in coordination includes beat contracting (PS), transition time-to-advanced, and two-stage transition time-to-advanced (TS).

### **1. INTRODUCTION EXAMPLE**

As a result of late enhancements in Cmos producing scale, rapid semiconductors, and lower supply voltage, time goal is turning out to be more prevalent than voltage goal [1], [2]. ADPLLs, space logical programming, jitter computations, and different applications have as of late profited from the utilization of a chance to-computerized converter (TDC). It's likewise used to figure high-accuracy flight times, which are turning out to be more incessant as TDC effectiveness improves.

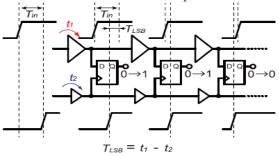

Fig. 1. Simplified schematic of a typical Venire TDC.

Two instances of testing applications are the laser range locater [3] and mass spectrometry [4]. It is normal utilized in imaging frameworks for fluorescence lifetime [5]. Fine fleeting exactness and a huge unique reach are needed in these applications, which are the examination's fundamental objective applications [6]. The general estimation proficiency is determined by the TDC, in this way a couple of PHS time goals with low jitter at various MS/s samplingrates are constantly required. A few time change procedures with sub-door defer goal have been proposed as far as fine goal. In view of the adaptability of its plan thought, the Venire TDC is widely used [6]-[9].

Professor<sup>1,2,3,4</sup> Assistant Professor<sup>1,2,3,4</sup>, Associate Professor<sup>1,2,3,4</sup>, Department of CSE Engineering, Pallavi Engineering College, Mail ID:krishna.cseit@gmail.com, Mail ID:drrajucse@gmail.com, Kuntloor(V),Hayathnagar(M),Hyderabad,R.R.Dist.-501505. An ordinary Venire TDC needs two separate postpone lines, which are for the most part associated as ring defer lines to save space, as displayed in Fig. 1. The underlying time span Tin diminishes when the lower defer line gets up to speed to the higher postpone line's change in light of the fact that the defer phases of two postpone lines, for example, t1 and t2, vary (t2 t1). We might get specific time goal by changing the defer differentiation TLSB = t1-t2. This plan, then again, comprises of two separate postpone lines with an underlying confound.

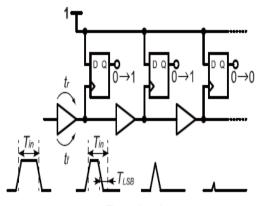

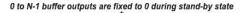

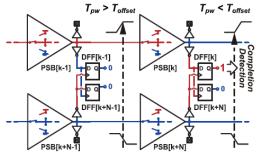

As displayed in Fig. 2 [10], [11], the beat contracting (PS) TDC is a sort of Venire TDC that uses the defer hole among rising and bringing down cradle advances rather than two separate postpone lines.

At the point when the info beat width diminishes TLSB = tryt f as it proliferates through each cushion level, the cradle is expected to create differing rise and fall delays, for example, pattern t f. (t f attempt). Rather than Venire's TDCs,

$T_{LSB} = t_r - t_f$

Fig. 2. Simplified schematic of a typical PS TDC.

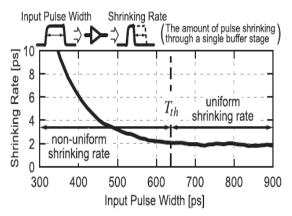

Fig. 3. Simulated PS rate versus input pulse width.

Until recently, TDCs have been built with precision time resolution in mind. It may, however, become

unattractive over a broad dynamic range. Venire TDCs with an N-bit resolution and a 2N dynamic spectrum, for example, have 2N delay elements and a 2N dynamic spectrum. The dynamic spectrum is halved when the temporal resolution is cut in half. The TDC needs additional 2N delay components to retain the same dynamic range, which increases area occupancy, lowers conversion rate, and increases jitter accumulation as N rises. One of the major ideas for enhancing dynamic range while avoiding a rise is a looping TDC design [13]. The number of cycles the loop's start signal rotates before the stop signal catches up is determined by a loop counter. Using the counter performance and the thermometer code given by the DFFs, the total conversion result may be determined. The input spectrum may be obtained in the best-case scenario.

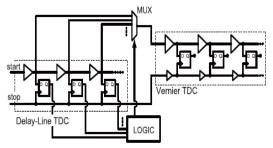

Fig. 4. Schematic of a typical TS TDC [14], [15].

Up to this point, TDCs were worked in light of specific time goal. It might, notwithstanding, become ugly over a wide powerful reach. At the point when Venire TDCs have a N-bit goal and a 2N powerful range, for instance, they have 2N postpone components and a 2N unique range. The unique range is divided when the fleeting goal is sliced down the middle. The TDC needs extra 2N postpone parts to hold a similar unique reach, which expands region inhabitance, brings down transformation rate, and builds jitter gathering as N rises. Quite possibly the most widely recognized techniques to work on powerful reach while keeping away from an ascent is to utilize a circling TDC plan [13]. The quantity of cycles the circle's beginning sign pivots before the plug signal gets up to speed is controlled by a circle counter. Utilizing the counter exhibition and the thermometer code given by the DFFs, the all out change result not really set in stone. The info range might be acquired in the most ideal situation.

N to 2N-1 buffer outputs are fixed to 1 during stand-by state

*Fig. 5. Block diagram of the proposed fine TDC based on the PSBR.*

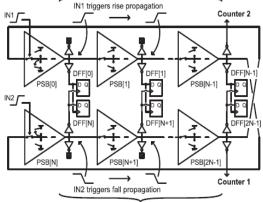

Fig. 6. Detailed schematic of the PSB.

The remainder of this article will be coordinated in the accompanying way. Segment II portrays the arranged TDC's plan and transformation thought. Segment III presents the arranged TDC circuit execution just as post-design reproduction discoveries. Segment IV wraps the examination up.

# 1. PROPOSED TDC ARCHITECTURE IN TWO STEPS

#### TDC Fine-Stage Pulse-Shrinking

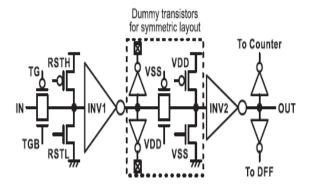

Figure 5 portrays the fine-stage TDC's PS buffering (PSBR)- based square chart. The greater part of PS supports with 2N stages are comprised of these segments (PSBs). The (N + k) Th PSB yield is associated with both the (N + k) Th and Kth DFF information inputs on the contrary side of the ring, while the Kth PSB yield (k = 0, N 1) is associated with both the Kth DFF information input and the (N + k) Th DFF clock input. Outside of the PSBR's

center, the PSBR's (N-1) and (2N-1) yields are connected to counters.

Fig. 7. Timing diagram of the PS TDC.

As the spreading beat width T pw matches the underlying implicit offset beat width Offset, the Kth PSB yield rises later than the falling edge of the (N + k)this yield, and the Kth DFF changes its yield from 0 to 1, as delineated in Fig. 8. This TDC distinguishes the principal worked in Offset and triggers the fruition cautioning by delivering this DFF yield progress. As an outcome, in spite of the fact that T offset changes because of technique contrasts, the total worth of Offset has no impact on the transformation interaction. Since T offset is chosen of course to fulfill Offset>Th in Fig. 3, the non-uniform shrinkage rate issue would no affect the proposed TDC.

Fig. 8. Detailed PSBR schematic at the moment of the completion of conversion.

Fig. 9. Block diagram of the proposed TS TDC.

#### B. Architecture of the Two-Step TDC

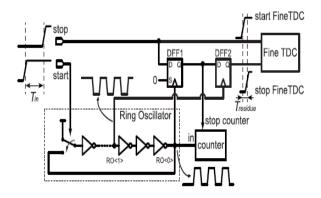

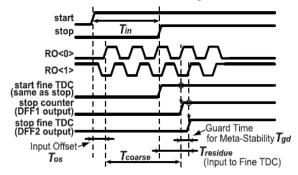

The recommended TS TDC design is displayed as a square outline in Figure 9. A ring oscillator incorporates a counter.

The PS TDC goes about as the coarse TDC in Section II, some time the PS TDC fills in as the fine stage. The proposed TDC, dissimilar to customary TS TDCs, joins the two TDCs with two DFFs to stay away from the between stage multiplexers from becoming non-ideal. Albeit the fine TDC-connected second DFF, DFF2, in Fig. 9, is by all accounts pointless, it tackles a huge strength issue in DFF1 brought about by offbeat time among RO0 and the info stop signal. In Section II-worked in C, the two DFFs are likewise used in the tuning interaction.

Fig. 10. Timing diagram of the proposed TS TDC.

It acts as a timer to keep the competition on track. The period residue produced by this roundup, Residue, is injected for fine transfer into the second stage TDC using the above-mentioned technique. Finally, using the formula below, the total input time period is calculated:

$$T_{\rm in} = T_{\rm os} + T_{\rm coarse} + T_{\rm gd} - T_{\rm residue}$$

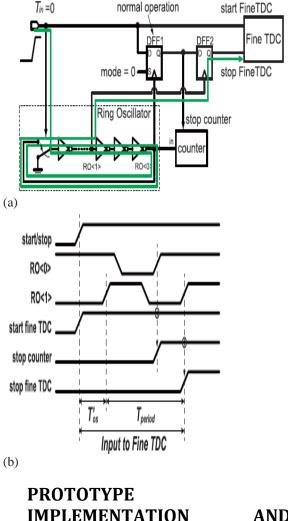

#### **C. Built-In Coarse Gain Calibration**

The gadget's underlying estimation measure is utilized to recognize the best adjustment strategy. Separation the time-frame relating to 1 LSB of the coarse TDC when span comparing to 1 LSB of the fine TDC to get the vital goal proportion. Utilizing DFF1's S (Fixed) information, which is utilized to set its yield Q to huge, two option pathways are exchanged during the adjustment stage, as outlined in Figures 11 and 12. Most importantly, until the alignment mode starts, the contribution of the principal stage inverter is set to GND. The fine TDC is halted after one coarse wavering period in addition to the info offset time T, as demonstrated in the circumstance outline, when DFF1 is in ordinary mode with a 0 contribution to the S-port, as displayed in Fig. 11. (a).

# IMPLEMENTATION AND SIMULATION

As displayed in Fig. Thirteen, the proposed TS TDC is built in 0.18-m ordinary CMOS innovation, and its, and are approved utilizing post-design copying.

TDC Fine-Stage A will be a sort of TDC.

In the lower half of Fig. 13, the PSB position in the fine TDC of the PSBR center, which has 32 PSB stages, is shown. To relax the DFF relations displayed in Fig. 5, the Kth PSBs (k = 0,..., 15) and (k

+ 16) are situated so that between PSB association wire lengths are equivalent. The semiconductor size and current utilization of PSB inverters should be painstakingly chosen because of the meaning of recognizing the impact of jitter development and assembling variety. The semiconductor sizes for the PSB were determined utilizing eel's jitter research.

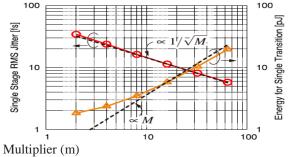

Work on schematic-level demonstrating with a solitary stage PSB jitter and energy for a solitary increment change dependent on semiconductor width (Fig. Fig. Gracious. 14). In PSB for INV1, Wombs = 8.32 = M am and Winos = 4.00 = M am. For INV2, Wombs = 8.00 M am and Winos = 4.00 M am. 1024 Monte Carlo runs of warm commotion reproductions were utilized to decide the rams jitter. The jitter, or beginning clamor on the yield capacitor, is brought about by the repetitive sound by the channel's obstruction [17].

$$\sigma_{t_{\rm dP}} \approx \sqrt{\frac{4kT\gamma_P t_{\rm dP}}{I_P (V_{\rm DD} - V_{\rm tP})}} \tag{3}$$

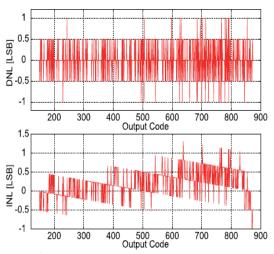

Fig. 16. Simulation results of DNL and INL of the fine-stage PS TDC.

#### **B. Two-Step TDC**

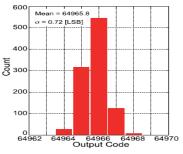

In the coarse TDC ring oscillator, which has 15 inverter arranges, the jitter investigation from [17] is used to decide semiconductor sizes. We utilized schematic-level recreation to confirm the examples of jitter and energy for a solitary increment change for the coarse stage ring oscillator by clearing the semiconductor distance, as displayed in Fig. 17. At the point when the reproduction impacts are set to M = 16, the dark specked lines are standardized. Jitter and energy are clearly connected to 1/M and M, individually, since the coarse amazing oscillator uses straightforward inverters. It can cover a range of up to 7 pieces since the coarse stage in our TS TDC can cover a range of up to 7 pieces.

Fig. 17 Post-layout simulation result of single-shot code distribution of the TS TDC.

Complete the transformation. For this situation, the fine stage retains 47.8% of the all out power, while the coarse stage ingests the rest. A reenacted DNL and INL are displayed in Figure 19. Because of the fairly lopsided shape brought about by the alignment flaw of the TDC's exchange trademark, the recreation range is in the focal point of the information time span range when the INL arrives at its greatest. Figure eighteen portrays the range's entire progress work. The DNL and INL of the TDC were 1.0/+1.0 LSB and 2.0/+1.0 LSB, separately.

| Ref.                                          | TCAS'14 [6] | JSSC 10 [7] | MEJ°15 [9]                                           | JSSC 12 [18] | JSSC*13 [19]            | JSSC'14 [20] | ASSCC'16 [11]           | This work   |

|-----------------------------------------------|-------------|-------------|------------------------------------------------------|--------------|-------------------------|--------------|-------------------------|-------------|

| Architecture                                  | 3D Vernier  | 2D Vernier  | Vernier<br>Sub-Ranging                               | Cyclic       | Two-Step<br>(Time Amp.) | Pipeline     | Pulse Shrinking<br>(PS) | Two-Step PS |

| Tech. [nm]                                    | 130         | 65          | 130                                                  | 130          | 65                      | 65           | 180                     | 180         |

| (Meas./Sim.)                                  | Meas.       | Meas.       | Meas.                                                | Meas.        | Meas.                   | Meas.        | Meas.                   | Sim.**      |

| Resol. [ps]                                   | 7           | 4.8         | 5                                                    | 125          | 3.75                    | 1.12         | 1.8                     | 2.00        |

| Precision rms [ps]                            | 20.8        | -           | 2.05                                                 | ~1.25*       | •                       | 0.77         | 2.16                    | 1.44        |

| (Tin at the meas. or sim.)                    | (@1.4ns)    |             | (0~300 ps)                                           | (@40ps)      |                         | (@~348ps*)   | (@860 ps)               | (@129.5 ns) |

| Rate [MS/s]                                   | 25          | 50          | 20                                                   | 50           | 200                     | 250          | 4.4                     | 3.3         |

| Range [bit]                                   | 11          | 7           | 6                                                    | 8            | 7                       | 9            | 9                       | 16          |

| DNL [LSB]                                     | 0.8         | 1           | 0.63                                                 | 0.7          | 0.9                     | 0.6          | 1.2                     | 15          |

| INL [LSB]                                     | 15          | 3.3         | 1.47                                                 | 3.0          | 23                      | 1.7          | 8.7                     | 42          |

| Power [mW]                                    | 0.33(@1MHz) | 1.7         | 1.15                                                 | 4.3          | 3.6                     | 15.4         | 3.4                     | 18.0        |

| Area [mm <sup>2</sup> ]                       | 0.28        | 0.02        | 0.7                                                  | 0.07         | 0.02                    | 0.14         | 0.07                    | 0.08        |

| FoM [pJ/convstep]                             | 0.40        | 1.14        | 1.96                                                 | 134          | 0.46                    | 0.32         | 14.6                    | 0.43        |

| k . I. I. J. Level A. Barre of A. annound and |             |             | ## Marte Cale simpleiter confederation is downer PAI |              |                         |              |                         |             |

\* calculated from the figure of the measurement result. \*\* Monte-Carlo simulation result that leads to the worst FoM.

Table I looks at the proposed TS TDC's proficiency to that of other recently announced sub-entryway defer goal TDCs. To build up a reasonable examination, the figure of legitimacy (Form), which is broadly utilized for TDC correlation, is utilized.

[6], [19], and [20] are presently being used. As an outcome, the Type has acquired inescapable acknowledgment.

$$FoM = \frac{Power}{(2^{N_{linear}} \times f_s)}$$

(6)

Where the effective number of linear bits (*L*inear) is given by

$$N_{\text{linear}} = \text{Range [bit]} - \log_2(\text{INL} + 1).$$

(7)

The Monte Carlo reproduction results for the proposed TDC's most pessimistic scenario M are shown. In view of current 0.18-m CMOS innovation, the recommended TDC offers a super wide reach and exact time accuracy, bringing about a serious Form.

# **2. CONCLUSION**

This page examines a wide scope of contributions just as fine-time goal blending procedures like PS and TS.To forestall an unwanted non-consistency of heartbeat shrinkage rate in the fine-stage PS TDC, customary PS TDCs utilize an extraordinary heartbeat infusion with an implicit offset beat and an offset beat width location system. Accordingly, fine goal and low-jitter time-to-advanced transmission, just as the PS TDC framework's benefits, like little region arrangement, are figured it out. The recommended TS configuration is added to the PS TDC to enlarge the info range. The useful issue initiated by the non-ideality of between stage signal spread course and the addition distinction between the two levels is tended to by the proposed TS TDC, which incorporates an inherent coarse increase adjustment system. As per the recreation, the recommended TDC could give 16-bit wide powerful reach and 2.0-ps fine goal simultaneously. It is feasible to get a cutthroat From. Dissimilar to recently revealed TDCs with sub-entryway defer goal and develop 0.18-m innovation, this TDC has a subdoor postpone goal and develop 0.18-m innovation.

#### REFERENCES

[1] R. B. Staszewski et al., "All-digital TX frequency synthesizer anddiscrete-time receiver for Bluetooth radio in 130-nm CMOS," IEEE J. Solid-State Circuits, vol. 39, no. 12, pp. 2278–2291, Dec. 2004.

[2] K. Asada, T. Nakura, T. Iizuka, and M. Ikeda, "Time-domain approach for analog circuits in deep sub-micron LSI," IEICE Electron. Express, vol. 15, no. 6, pp. 1–21, 2018.

[3] P. Palojärvi, K. Määttä, and J. Kostamovaara, "Integrated time-of-flight laser radar," IEEE Trans. Instrum. Meas., vol. 46, no. 4, pp. 996–999,

Aug. 1997.

[4] K. Sano et al., "Design and high-speed tests of a single-fluxquantum time-to-digital converter for time-of-flight mass spectrometry," in Proc. IEEE 14th Int. Superconductive Electron. Conf. (ISEC), Jul. 2013, pp. 1–3.

[5] M.-W. Seo et al., "A 10 ps time-resolution CMOS image sensor withtwo-tap true-CDS lock-in pixels for fluorescence lifetime imaging," IEEE J. Solid-State Circuits, vol. 51, no. 1, pp. 141–154, Jan. 2016.

[6] Y. Kim and T. W. Kim, "An 11 b 7 ps resolution two-step time-to digital converter with 3-D Vernier space," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 61, no. 8, pp. 2326–2336, Aug. 2014.

[7] L. Vercesi, A. Liscidini, and R. Castello, "Two-dimensions Vernier time-to-digital converter," IEEE J. Solid-State Circuits, vol. 45, no. 8, pp. 1504–1512, Aug. 2010.

[8] B. Markovic, S. Tisa, F. A. Villa, A. Tosi, and F. Zappa, "A high-linearity,17 ps precision time-to-digital converter based on a single-stage Vernier delay loop fine interpolation," IEEE Trans. Circuits Syst. I, Reg. Papers,

vol. 60, no. 3, pp. 557-569, Mar. 2013.

[9] C.-T. Ko, K.-P. Pun, and A. Gothenberg, "A 5-ps Vernier subranging time-to-digital converter with DNL calibration," Microelectron. J., vol. 46, no. 12, pp. 1469–1480, Dec. 2015.

[10] C.-C. Chen, S.-H. Lin, and C.-S. Hwang, "An area-efficient CMOS timeto- digital converter based on a pulse-shrinking scheme," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 3, pp. 163–167, Mar. 2014.

[11] T. Iizuka, T. Koga, T. Nakura, and K. Asada, "A fineresolution pulse shrinking time-to-digital converter with completion detection utilizing built-in offset pulse," in Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC), Nov. 2016, pp. 313–316.

[12] P. Chen, S.-I. Liu, and J. Wu, "A CMOS pulse-shrinking delay element for time interval measurement," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 47, no. 9, pp. 954–958, Sep. 2000.

[13] J.-P. Jansson, A. Mäntyniemi, and J. Kostamovaara, "A CMOS time-to-digital converter with better than 10 ps single-shot precision," IEEE J. Solid-State Circuits, vol. 41, no. 6, pp. 1286– 1296, Jun. 2006.

[14] V. Ramakrishnan and P. T. Balsara, "A wide-range, highresolution, compact, CMOS time to digital converter," in Proc. 19th Int. Conf. VLSI Design (VLSID), Jan. 2006, pp. 197–202.

[15] S. Henzler, Time-to-Digital Converters. Amsterdam, The Netherlands: Springer, 2010.